Todo el propósito del computador es obtener resultados a partir de datos que le proporcionamos. Es obvio entonces que necesitaremos mecanismos para para proporcionar los datos (entrada) y para recibir los resultados (salida). Existe en efecto una creciente diversidad de dispositivos de entrada y de salida. Entre los dispositivos de entrada más conocidos está el teclado y el ratón, pero lo son también: el joystick, controladores de juegos, micrófono, cámara, puertos de red. trackball, lightpen, scanner, lectores ópticos, lectores magnéticos, lectores de códigos de barra, sensores (típicamente conversores análogo/digital).

Los dispositivos de salilda más conocidos son el monitor y la impresora. Hay varias tecnologías tanto para los monitores (CRT, LED, LCD) como para impresoras (de caracteres, de línea, de página, chorro de tinta, lasser). Otros dispositivos de salilda son: parlantes, auriculares, televisores, proyectores, plotter.

Algunos dispositivos cumplen función tanto de entrada como de salida, como los modem, que convierten señales telefónicas en señales digitales y sirven tanto para recibir como para enviar datos a través de la red telefónica. Así también las tarjetas de red, para enviar y recibir paquetes de datos según los protocolos de red. Ambos de estos dos últimos dispositivos mencionados son esenciales para la comunicación a grandes distancias entre computadores.

Un pen-drive es también un dispositivo capaz de recibir y de enviar información; sin embargo, es más apropiado clasificar este tipo de dispositivos como memorias (a veces llamadas memorias externas o terciarias). Otros ejemplos de esta clase de memoria son el CD y el DVD, discos flexibles, cintas magnéticas y cintas de papel. Todos estos últimos prácticamente desaparecidos hoy día. En cuanto a los discos duros magnéticos, son sin duda de entrada y salida pero se les considera definitivamente como memoria, es la llamada memoria secundaria, son un depósito de grandes cantidades de información, tanto de datos como de programas, pero no cumplen la función de comunicación con el humano o con otro computador, de modo que no los llamamos de entrada/salida.

Hasta aquí, sólo hemos hecho un recorrido sobre la variedad de dispositivos de E/S existentes; veamos ahora cómo ocurre la transferencia de información entre ellos y el CPU. El hardware de E/S suele separarse en dos piezas: el dispositivo propiamente dicho y una interfaz, esta última es donde residen los registros a los cuales hacen referencia las instrucciones de E/S y donde se compatibiliza los niveles y tecnología de señal que vienen del dispositivo con los que utiliza el computador. Básicamentne, hay tres modos diferentes de comunicación: E/S programada, E/S por interrupciones y acceso directo a memoria (DMA).

En la E/S programada se utiliza las instruciones de E/S que ofrezca la arquitectura, típicamente IN puerto y OUT puerto, donde el puerto hace referencia al registro de la interfaz donde se recibe el dato a leer, o donde se carga previamente el dato a enviar. Las interfaces de E/S ofrecen, además del puerto de datos al que nos hemos referido, un segundo puerto, el puerto de status, donde particulares bit de ese registro indican la condición actual del dispositivo, como «ocupado», «libre», «con error» y otros posibles indicadores. También podemos encotrar un tercer puerto, el puerto de control, donde enviamos órdenes especiales al dispositivo. Tales írdenes son muy variadas y dependen mucho del tnpo de dispositivo. Sopn ejemplos las órdenes de inicialización, de definir modo y velocidad de transferencia, etc. Típicamente una operación de E/S comienza por consultar el bit de ocupado en el registro de status: si indica «libre» se procede a transferir el dato; de lo contrario debe esperar hasta que esté «libre». En la E/S programada, esta espera es «ocupada», se designa así a un lazo en el cual se sigue consultando el bit de «ocupado» hasta que indique que está «libre». En ese momento, se ejecuta la instrucción de E/S. Veamos el esquema general de una secuencia de lectura de un caracter:

wait: SKIP on bit set <status port>

JUMP wait

IN <data port>

Una operación de entrada/salida puede ser muy lenta comparada con la velocidad del CPU. Pensemos por ejemplo en un usuario que teclea una linea de texto. Entre cada caracter y el siguiente puede transcurrir 1/12 de segundo (si es que escibe a velocidad de mecanógrafo), tiempo suficiente para que un CPU ejecute unas doscientas mil instrucciones (o mucho más en un RISC-V por ejemplo). En la secuencia que acabamos de mostrar, el lazo de espera ocupada puede dar centenares de miles de vueltas antes de salir para transferir el dato (típicamente un byte). Esa disparidad de velocidades ha dado lugar a las otras estrategias de E/S. Sin embargo, para entender el rationale detrás de esos métodos es necesario introducir el concepto de multiprogramación: un tema, cuyos detalles pertenecen más a un curso sobre SO y no a uno de OAC. La necesaria comprensión de la idea de multiprogramación la introduciremos de inmediato y la desarrollaremos un poco más en la lección No. 18.

Ese tiempo perdido en la espera ocupada (centenares de miles de instrucciones de máquina entre cada caracter que tecleamos y el siguiente) es difícil aprovecharlo en el mismo programa que hace la operación de E/S. Si el programa está leyendo un dato, quizá no pueda avanzar en ningún otro cómputo hasta que no le llegue el dato; es más, si espera digamos un número, debe esperar no sólo por un particular dígito de ese número, sino por el número completo, por todos su digitos. Debemos pues imaginar un lazo más externo, que contiene al lazo de espera, en el cual se van acumulando los dígitos hasta completar (quizá señalado por el arribo del código ENTER) el número o dato de interés. Un programador podría ingeniárselas para ir avanzando en otros procesamientos de su programa mientras llega el dato que necesita en otra parte del mismo programa; sin embargo se trata de un tipo complejo y delicado de programación: programación concurrente. Una solución universalmente adoptada es más bien la multiprogramación. Ya que todos o la mayoría de los programas necesitan realizar E/S, de hecho algunos son intensivos en E/S, por que no mantener en memoria un grupo de programas (no relacionados entre si) y cuando uno de ellos requiere un dato, pasar el control del CPU a otro de los programas, para que avance en su procesamiento mientras el primero espera el dato. Cuando el segundo programa requier E/S se volvería a dar chance a otros de los programas en la ronda de multiprogramación, eventuialmente al primero, al que había cedido el CPU al segundo, si es que ese primero ya recibió el dato que esperaba. Así varios programas avanzan concurrentemente, mientras unos esperan datos, otro utiliza el CPU. El mismo razonamiento aplica a los proceso de salida. El software encargado de hacer esta conmutación de programas (o, más apropiadamente, como veremos en la lección 18, conmutación de procesos) es una parte importante del SO, el catalogador y despachador de procesos. La multiprogramación es la técnica más efectiva para incrementar el throughput del computador, esto es la cantidad de tareas completadas por unidad de tiempo, y lo logra aprovechando los tiempos muertos de CPU que generarían las esperas por entrada/salida.

Entrada/salida controlada por interrupciones

Hay una complicación. Si bien el proceso de E/S es, como dijimos, bien lento comparado con la velocidad del CPU, es sin embargo un proceso que puede requerir atención urgente: apenas hay un dato listo en el puerto de entrada, debemos moverlo de ese puerto a un lugar seguro en memoria, de lo contrario puede venir un nuevo dato, que borrará el actual valor que estuviese en el puerto de datos. En otras palabras, todo dato que arribe al puerto de entrada debe ser copiado a una celda de memoria antes de que arribe un nuevo dato. Esto es así porque la mayoría de los dispositivos de entrada operan de manera asíncrona respecto al CPU. Con las operaciones de escritura, puede no ser tan crítico el vaciado del puerto de salida, al fin y al cabo es el CPU el que decifde cuando poner algo allí, el dispositivo exterfno sólo tiene que «absorberlo» , sin embargo el mecanismo de atención que descibiremos en seguida para manejar la necesidad de atender el arribo de datos de entrada se aplica igualmente para datos de salida dado que trae grandes ventajas para la implementación de multiprogramación.

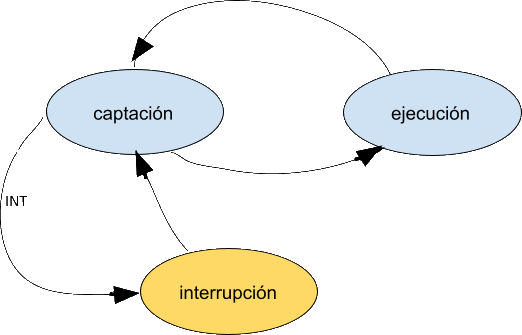

Para implementar un mecanismo que permita atender el evento de E/S completada se modifica el ciclo de captación/ejecución (explicado en la lección 5) extendiéndolo con la fase de interrupción. El diagrama de estados para el nuevo ciclo es el siguiente:

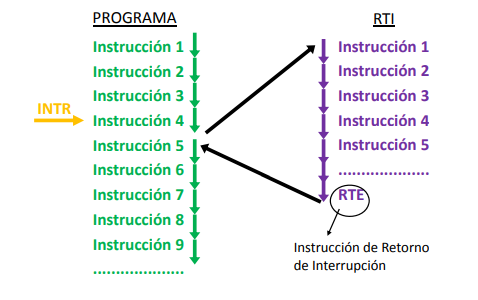

Hemos agregado la fase de interrupción. A esta fase se entra, desde la fase de captación, al activarse la señal INT. El hardware de esta fase coloca en el IR el código de una instrucción de CALL a una dirección resevada para un subprograma de manejo de interrupción. Dicho subprograma hará lo que corresponda según el tipo de operación de E/S de que se trate. Para el ejemplo simple de un dispositivo que coloca bytes en un puerto de entrada, lo que hará es: salvar el estatus del procesador (luego veremos qué significa eso) mover ese byte a un arreglo en memoria; apuntar al siguiente elemento del arreglo (preparándose para una eventual nueva interrupción por el arrivo de otro caracter), restaurar el estatus y retornar. Al retornar va a continuar desde el punto en el programa donde se produjo la interrupción. Como se ve el programa interrumpido simplemente sufrirbá un pequeño retraso en su ejecución. Decimos pequeño porque las instrucciones en un típico subprograma de manejo de interrupciones son muy pocas (como mover un byte de registro a un arreglo en memoria e incrementar el índice del arreglo). Si el manejador de interrtupciones necesita hacer otras operaciones que alteren algún registro del procesador, debe primero guardar los valores que había en esos registros al momento de entrar al manejador y restaurarlos justo antes de retornar, sólo de esa manera podrá el programa interrumpido continuar -despues de haberse atendido la interrtupción- como si nada hubiese pasado. Los valores en los registros en un momento dado es lo que se llama el estatus del CPU en ese momento. Por eso decimos que los manejadores de interrupción deben salvar y restaurar el estatus.

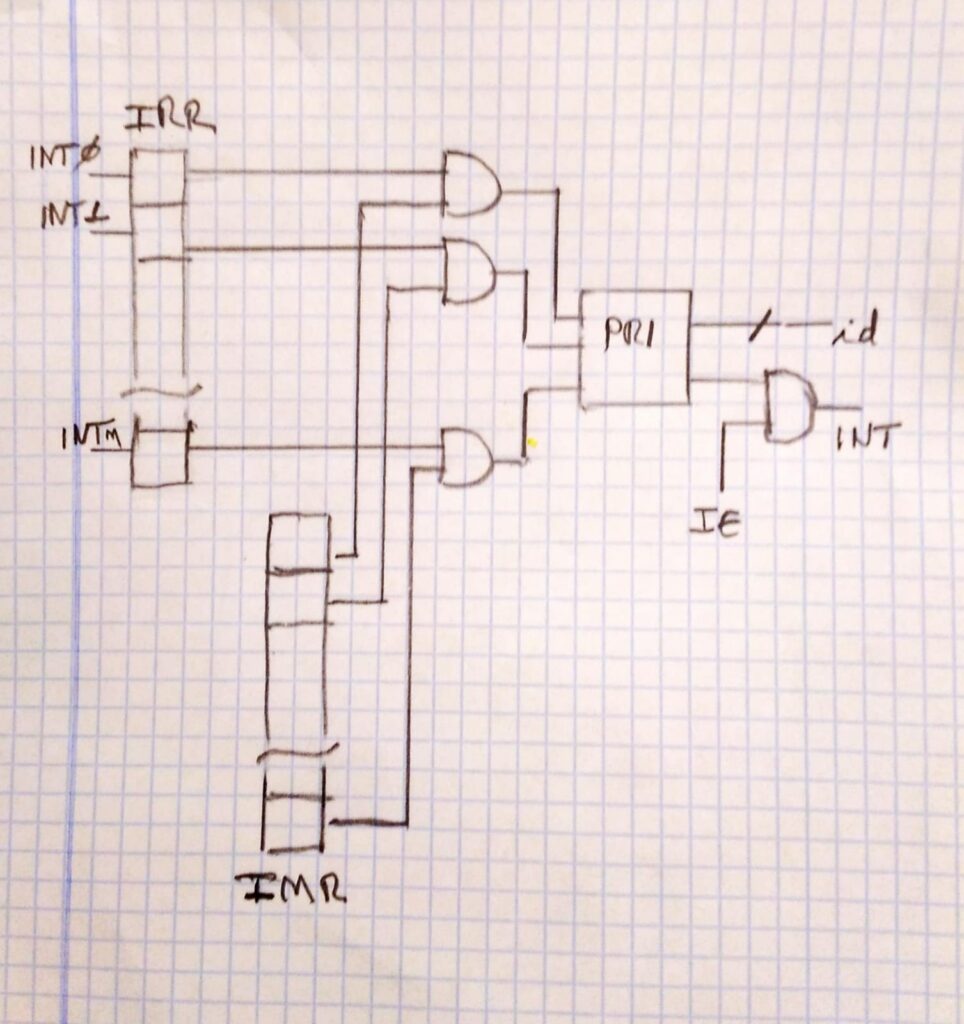

Las interrupciones pueden venir de cualquiera de los dispositivos de E/S (y aún de otras fuentes, como veremos luego). Cualquiera de ellas puede generar la señal INT que llega al CPU. Es más, siendo las interrupciones señales asíncronas, podrían venir varias al mismo tiempo, las cuales habrá que ir atendiendo, una por una, según cierto orden de prioridades o urgencia. Es importante que el CPU, además de recibir la petición de interrupción, pueda determinar de cuál dispositivo vino esa interrupción. Una vez aceptada la interrupción se pasará control a la rutina de manejo específica para las características del dispositivo que la solicitó. La figura que sigue representna el hardware que ofrece estas funcionalidades. Las señales de requerimiento de interrupción (Interrupt Request) provenientes de los dispositivos (y otras fuentes) son latchadas en el Registro de Servicio de Interrupción (ISR), pasan a un banco de compuertas AND que las dejará seguir o no según lo indique cada bit del Registro de Máscaras (IMR), entrán así a un Codificador de Prioridad, el cual tiene como salidas la señal de interrupción y la identificación de la fuente interruptora. En caso de que hubiese más de un requerimiento de interrupción al mismo tiempo, la identificación corresponderá a la de más alta prioridad. La salida de interrupción es todavía pasada por otra cpompuerta AND donde puede ser controlada por una señal, IE (Interrupt Enable) de deshabilitar/habilitar las interrupciones.

El repertorio de instrucciones debe incluir instrucciones de control para el sistema de interrupciones. Por una parte CLI, STI para deshabilitar o habilitar el sistema de interrupciones en general; esto es, para poner en «0» o en «1» la señal IE. Otras instruciones, como Set Interrupt Mask, SIM <máscara>, permiten escribir el registro de máscaras, de modo de deshabilitar/habilitar requerimientos específicos de interrupción. Es usual que cuando el CPU pasa control al manejador de interrupciones, las interrupciones estén automáticamente deshabilitadas; el manejador podría decidir dejarlas deshabilitadas y completar su trabajo -que para la mayoría de los dispositivos son pocas instrucciones- sin ser nuevamente interrumpido; o podría habilitar interrupciones (STI), permitiendo de esa manera interrupciones anidadas. (dibujo de nido de int) Otras instrucciones permiten leer y escribir el ISR. Se lee para saber cuáles otras fuentes están solicitando interrupción; se escribe para apagar el bit correspondiente a la interrtupción que se está sirviendo, es decir que ya no está pendiente de servicio (esto podría hacerse al comienzo o al final del manejador de interrupciones, dependiendo de la estrategia en uso).

El mecanismo de interrumpciones se ha extendido más allá de su propósito de completar los procesos de E/S y constituye un recurso de tal importancia que, en algunas arquitecturas, el salvado/recuperación de estatus se ha implementado en hardware; es decir, es parte de las responsabilidades de la fase de «interrupción» (ver diagram de círculos y flechas que incluímos arriba para el ciclo ampliado captación/ejecución/interrupción).

Otras fuentes de interrupción: por tiempo, por software, excepciones, falla de potencia. Interrupciones anidadas. Page fault.

-

01 – Introducción

-

02 – Partes del Computador

-

03 – Memoria

-

04 – Registros

-

05 – Funcionamiento del Computador

-

06 – Formato de Instrucción

-

07 – Modos de Direccionamiento

-

08 – Repertorio de Instrucciones

-

09 – Trayectorias de Datos

-

10 – Entrada y Salida

-

11 – Velocidad de Procesamiento y Capacidad de Memoria

-

12 – Interrupciones

-

13 – Organización Tubular

-

14 – Memoria Cache

-

15 – Memoria Virtual

-

16 – Multiprocesadores

-

Post Template

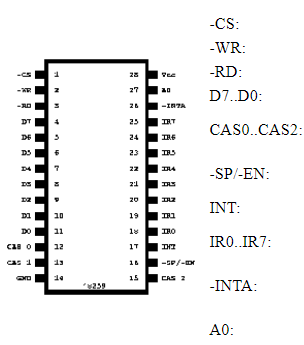

Hoy día, gracias a la miniaturización, todo el hardware de manejo de interrupciones está integrado en el chipset que conforma el CPU, pero en muchísmas de las computadoras personales hoy activas, está a cargo de un circuito integrado aparte, conocoido como PIC o Peripheral Interrupt Controller, el famoso chip 8259. Ese controlador implementa toda la funcionalidad descrita y permite, ya que es programable, otros criterios de manejo, como prioridades rotatorias.

Las líneas IR0..IR7 son 8 lineas de requerimiento de interupción provenientes de hasta 8 dispositivos externos. De haber más de 8 dispositivos externos, se utiliza otro (u otros) 8259 conectado en cascada a través de las líneas CAS. Siendo los requerimientos de interrupción asíncronos, puede ocurrir que llegue más de un requerimiento al mismo tiempo (varias líneas IR activas al mismo tiempo), en tal caso el 8259 aplica prioridades: las líneas IR más bajas tienen prioridad (IR0 > prioridad IR1, etc). La presencia de uno o más requerimientos de interrtupción activará la línea INT que va conectada a la entrada de solicitiud de interrupción en el CPU (la señal llamada tambien «INT» en el diagrama de fases F/I/E). El CPU responde enviando la señal de reconocimiento de interrupción: -INTA (interrupt acknowledgement). En este momento el 8259 activa el bit cortrespondiente a la interrupción a procesar en uno de sus registros internos, el ISR (Interrupt Service Register) y apaga el correspondiente bit en el otro registro interno, el IRR (Interrupt Requests Register); en este último registro podrían haber otros bits encendidos, indicando que hay otras interrupciones (de menor prioridad de la que se va a atender ahora) pendientes de atención. Cuando el CPU envíe un segundo pulso -INTA, el 8259 apaga el bit correspondinete en el ISR y coloca en sus lineas D0..D7 un valor llamado (quizá inadecuadamente) vector de interrupción, que no es más que el identificador que permite saber cuál dispositivo fue el que interrupió y por tanto cuál rutina de manejo de interrupción debe atenderla.

Interrupciones en SUR

El mecanismo y el manejo de interrupciones en SUR está inspirado en una arquitectnura clasica de minicomputador, el HP2100.

Probar a organizar estas columnas con varias rows, para hacer coincidir en col izquierda y derecha los temas relacionados

Aquí iría texto relacionado con la columna izquierda

—-

Usar alineación superior para igualar lineas de comienzo.

—